fati2014

Newbie level 2

hello,

I am beginner with CMOS transistors circuit. I am currently working on a project that is based on transistors.

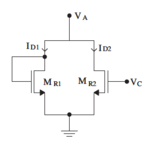

I'm working on sizing of NMOS transistors of attached file.

This circuit is an active resistance, but my problem is at the choice of parameters (W and L) of the circuit.

Can you help me to sized this circuit?

Kind regards.

I am beginner with CMOS transistors circuit. I am currently working on a project that is based on transistors.

I'm working on sizing of NMOS transistors of attached file.

This circuit is an active resistance, but my problem is at the choice of parameters (W and L) of the circuit.

Can you help me to sized this circuit?

Kind regards.