Soh_bhat

Junior Member level 1

Hi there,

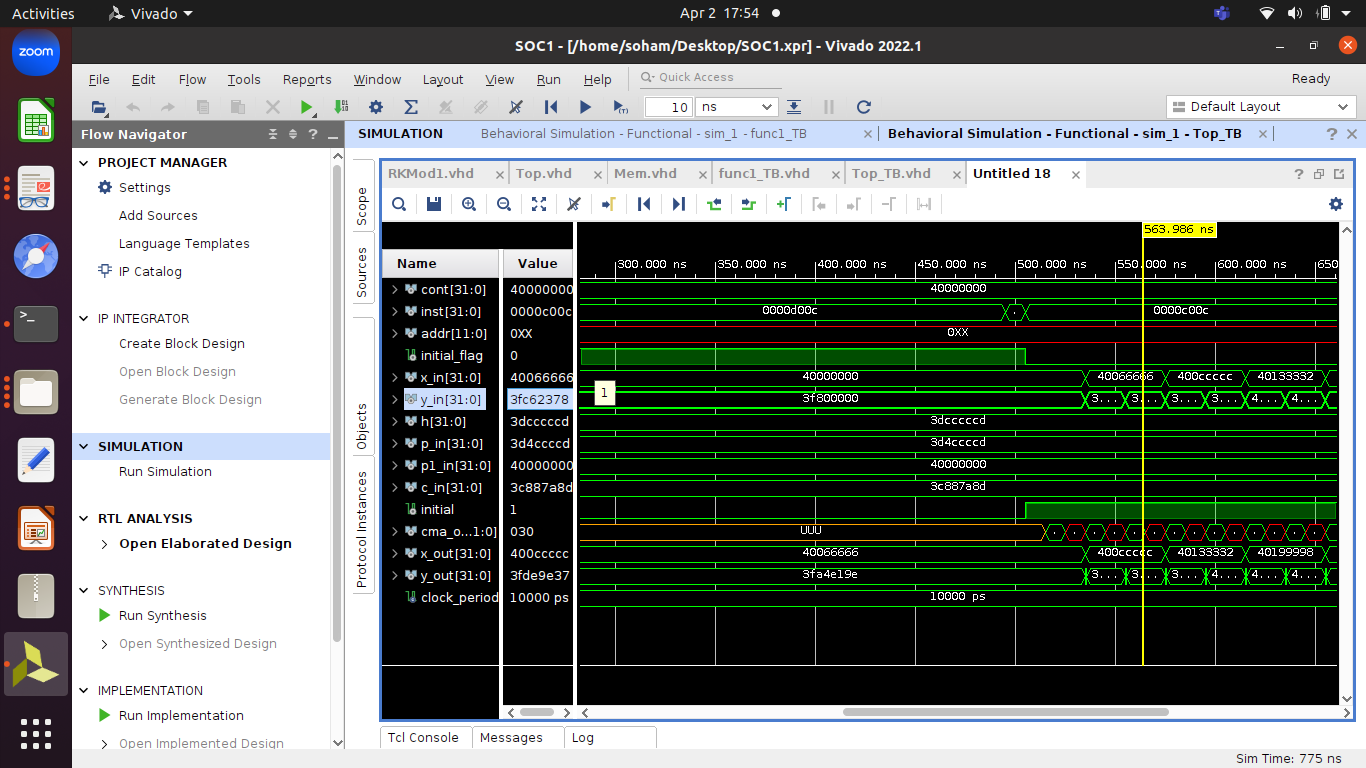

Can you check this top module and the test bench? I don't know if I am doing something wrong with the test bench or clock. Can you kindly help me modify it? The waveform is delivering the outputs correctly, but the output is split into two parts within a specific period. You can check the y_in and you can see there's two values in between the first x_in range. I want it to be in one range of x_in. Am I doing anything wrong with this code? Coz all the other modules are working perfectly fine as expected. Would be happy to share more details. Your help will be appreciated.

Top:

Can you check this top module and the test bench? I don't know if I am doing something wrong with the test bench or clock. Can you kindly help me modify it? The waveform is delivering the outputs correctly, but the output is split into two parts within a specific period. You can check the y_in and you can see there's two values in between the first x_in range. I want it to be in one range of x_in. Am I doing anything wrong with this code? Coz all the other modules are working perfectly fine as expected. Would be happy to share more details. Your help will be appreciated.

Top:

Code:

----------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 02/26/2023 07:30:53 PM

-- Design Name:

-- Module Name: Top - Behavioral

-- Project Name:

-- Target Devices:

-- Tool Versions:

-- Description:

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx leaf cells in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity Top is

Port (

--clock: in std_logic;

inst: in std_logic_vector(31 downto 0);

cont: out std_logic_vector(31 downto 0);

addr: out std_logic_vector(11 downto 0);

x_out: out std_logic_vector(31 downto 0);

y_out: out std_logic_vector(31 downto 0);

x_in: out STD_LOGIC_VECTOR(31 downto 0);

y_in : out STD_LOGIC_VECTOR(31 downto 0);

h : out STD_LOGIC_VECTOR(31 downto 0);

p_in : out STD_LOGIC_VECTOR(31 downto 0);

p1_in : out STD_LOGIC_VECTOR(31 downto 0);

c_in : out STD_LOGIC_VECTOR(31 downto 0);

initial: out std_logic;

initial_flag: out std_logic;

cma_out: inout std_logic_vector(11 downto 0)

);

end Top;

architecture Behavioral of Top is

component Mem is

Port (

cont: in std_logic_vector(31 downto 0);

addr : in std_logic_vector(11 downto 0);

x_in: out STD_LOGIC_VECTOR(31 downto 0);

y_in : out STD_LOGIC_VECTOR(31 downto 0);

h : out STD_LOGIC_VECTOR(31 downto 0);

p_in : out STD_LOGIC_VECTOR(31 downto 0);

p1_in : out STD_LOGIC_VECTOR(31 downto 0);

c_in : out STD_LOGIC_VECTOR(31 downto 0);

write_en: in std_logic;

clock: in std_logic;

flush : in std_logic;

init: in std_logic;

init_flag: in std_logic ;

x_out: in STD_LOGIC_VECTOR(31 downto 0);

y_out : in STD_LOGIC_VECTOR(31 downto 0);

cma_out: inout STD_LOGIC_VECTOR(11 downto 0)

);

end component;

component reg is

Port (

clk: in std_logic;

rs1 : in std_logic_vector(4 downto 0);

regwr : in std_logic;

wrdata: out std_logic_vector(31 downto 0)

-- x_out : out std_logic_vector(31 downto 0);

-- y_out: out std_logic_vector(31 downto 0)

);

end component;

component Control is

Port (

inst: in std_logic_vector(31 downto 0);

addr: out std_logic_vector(11 downto 0);

flush: out std_logic;

write_en: out std_logic;

init: out std_logic;

init_flag: out std_logic

);

end component;

component RKMod1 is

Port (

x_in: in STD_LOGIC_VECTOR(31 downto 0);

y_in : in STD_LOGIC_VECTOR(31 downto 0);

h : in STD_LOGIC_VECTOR(31 downto 0);

p_in : in STD_LOGIC_VECTOR(31 downto 0);

p1_in : in STD_LOGIC_VECTOR(31 downto 0);

c_in : in STD_LOGIC_VECTOR(31 downto 0);

x_out: out STD_LOGIC_VECTOR(31 downto 0);

y_out: out STD_LOGIC_VECTOR(31 downto 0)

--clk : in std_logic

--aclk: in std_logic

);

end component;

signal clock: std_logic := '1';

signal addr1: std_logic_vector(11 downto 0);

signal wdata: std_logic_vector(31 downto 0);

signal rs : std_logic_vector(4 downto 0);

signal flush : std_logic;

signal write_en: std_logic;

signal x_in1: STD_LOGIC_VECTOR(31 downto 0);

signal y_in1 : STD_LOGIC_VECTOR(31 downto 0);

signal h1 : STD_LOGIC_VECTOR(31 downto 0);

signal p_in1 : STD_LOGIC_VECTOR(31 downto 0);

signal p1_in1 : STD_LOGIC_VECTOR(31 downto 0);

signal c_in1 : STD_LOGIC_VECTOR(31 downto 0);

signal x_output: STD_LOGIC_VECTOR(31 downto 0);

signal y_output : STD_LOGIC_VECTOR(31 downto 0);

signal init : std_logic;

signal init_flag : std_logic;

--signal inst: std_logic_vector(31 downto 0);

signal clk_period: time := 10 ns;

begin

uut1: Mem port map (

cont => wdata,

addr => addr1,

write_en => write_en,

clock => clock,

init_flag => init_flag,

x_in => x_in1,

y_in => y_in1,

h => h1,

p_in => p_in1,

c_in => c_in1,

p1_in => p1_in1,

flush => flush,

init => init,

x_out => x_output,

y_out => y_output,

cma_out => cma_out

);

uut2: reg port map (

clk => clock,

rs1 => inst(19 downto 15),

regwr => write_en,

wrdata => wdata

);

uut3: Control port map (

inst => inst,

addr => addr1,

flush => flush,

write_en => write_en,

init => init,

init_flag => init_flag

);

uut4: RKMod1 port map (

x_in => x_in1,

y_in => y_in1,

h => h1,

p_in => p_in1,

c_in => c_in1,

p1_in => p1_in1,

x_out => x_output,

y_out => y_output

);

clk_process rocess

begin

clock <= '0';

wait for clk_period/2;

clock <= '1';

wait for clk_period/2;

end process clk_process;

cont <= wdata;

addr1 <= inst(31 downto 20);

addr <= addr1;

initial <= init;

x_in <= x_in1;

y_in <= y_in1;

h <= h1;

c_in <= c_in1;

p_in <= p_in1;

p1_in <= p1_in1;

initial_flag <= init_flag;

x_out <= x_output;

y_out <= y_output;

end Behavioral;

Test bench:

----------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 02/26/2023 08:02:34 PM

-- Design Name:

-- Module Name: Top_TB - Behavioral

-- Project Name:

-- Target Devices:

-- Tool Versions:

-- Description:

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx leaf cells in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity Top_TB is

-- Port ( );

end Top_TB;

architecture Behavioral of Top_TB is

component Top is

Port (

--clock: in std_logic;

inst: in std_logic_vector(31 downto 0);

cont: out std_logic_vector(31 downto 0);

addr: out std_logic_vector(11 downto 0);

x_out: out std_logic_vector(31 downto 0);

y_out: out std_logic_vector(31 downto 0);

x_in: out STD_LOGIC_VECTOR(31 downto 0);

y_in : out STD_LOGIC_VECTOR(31 downto 0);

h : out STD_LOGIC_VECTOR(31 downto 0);

p_in : out STD_LOGIC_VECTOR(31 downto 0);

p1_in : out STD_LOGIC_VECTOR(31 downto 0);

c_in : out STD_LOGIC_VECTOR(31 downto 0);

initial_flag: out std_logic;

-- init_flag: in std_logic;

initial: out std_logic;

cma_out: inout std_logic_vector(11 downto 0)

);

end component;

--signal clock: std_logic := '0';

signal cont: std_logic_vector(31 downto 0);

signal inst: std_logic_vector(31 downto 0);

signal addr : std_logic_vector(11 downto 0);

signal initial_flag: std_logic;

signal x_in: STD_LOGIC_VECTOR(31 downto 0);

signal y_in : STD_LOGIC_VECTOR(31 downto 0);

signal h : STD_LOGIC_VECTOR(31 downto 0);

signal p_in : STD_LOGIC_VECTOR(31 downto 0);

signal p1_in : STD_LOGIC_VECTOR(31 downto 0);

signal c_in : STD_LOGIC_VECTOR(31 downto 0);

signal initial: std_logic;

signal cma_out: std_logic_vector(11 downto 0);

signal x_out: STD_LOGIC_VECTOR(31 downto 0);

signal y_out : STD_LOGIC_VECTOR(31 downto 0);

constant clock_period : time := 10 ns;

begin

uut: Top port map (

--clock => clock,

inst => inst,

initial_flag => initial_flag,

cont => cont,

addr => addr,

x_in => x_in,

y_in => y_in,

h => h,

c_in => c_in,

p_in => p_in,

p1_in => p1_in,

initial => initial,

x_out => x_out,

y_out => y_out,

cma_out => cma_out

);

--clk_process rocess

-- begin

-- clock <= '0';

-- wait for clock_period/2;

-- clock <= '1';

-- wait for clock_period/2;

-- end process clk_process;

stimulus: process

begin

--write_en <= '1';

inst <= "000000000000" & "00001" & "000" & "00000" & "0001100"; --- RKI

wait for clock_period;

--write_en <= '1';

inst <= "000000000100" & "00010" & "000" & "00000" & "0001100";

wait for clock_period;

--write_en <= '1';

inst <= "000000001000" & "00011" & "000" & "00000" & "0001100";

wait for clock_period;

--write_en <= '1';

inst <= "000000001100" & "00100" & "000" & "00000" & "0001100";

wait for clock_period;

--write_en <= '1';

inst <= "000000010000" & "00101" & "000" & "00000" & "0001100";

wait for clock_period;

--write_en <= '1';

inst <= "000000010100" & "00110" & "000" & "00000" & "0001100";

wait for clock_period;

--wait for clock_period * 50.5;

inst <= "000000000000" & "00001" & "101" & "00000" & "0001100"; --- RKU (FLUSH)

wait for clock_period * 43.5;

--wait for clock_period * 14;

--wait for clock_period * 51;

inst <= "000000000000" & "00001" & "001" & "00000" & "0001100"; --- RKS

wait for clock_period;

inst <= "000000000000" & "00001" & "100" & "00000" & "0001100";---RKU(UPDATE)

wait for clock_period;

----wait for clock_period;

--wait for clock_period * 45;

--wait for clock_period * 20;

--wait for clock_period * 20;

wait;

end process;

end Behavioral;

Last edited by a moderator: