cupoftea

Advanced Member level 5

Hi,

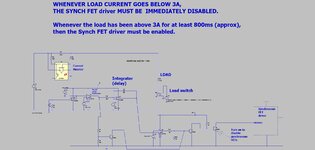

The attached circuit is for use with synchronous FET controllers for Bridge's/Forwards.

So, the attached is a circuit which disables a synchronous FET controller whenever the power supply loading goes below 30%.

This is needed to avoid reversing current in the output inductor, which then causes overvoltages when the synch FET goes OFF.

The circuit also re-enables the controller when loading goes >30%...but does this after a delay of some 1 second or so.

Please can you see any opportunities for reducing component count?

****EDIT.....my sincere apologies...i forgot i put this in the Analog section (as below) END OF EDIT*****

[please could the above thread be deleted from the Analog section if at all possible?....Apologies for this....i stupidly forgot i put it there.]

The attached circuit is for use with synchronous FET controllers for Bridge's/Forwards.

So, the attached is a circuit which disables a synchronous FET controller whenever the power supply loading goes below 30%.

This is needed to avoid reversing current in the output inductor, which then causes overvoltages when the synch FET goes OFF.

The circuit also re-enables the controller when loading goes >30%...but does this after a delay of some 1 second or so.

Please can you see any opportunities for reducing component count?

****EDIT.....my sincere apologies...i forgot i put this in the Analog section (as below) END OF EDIT*****

[please could the above thread be deleted from the Analog section if at all possible?....Apologies for this....i stupidly forgot i put it there.]