cupoftea

Advanced Member level 5

Hi,

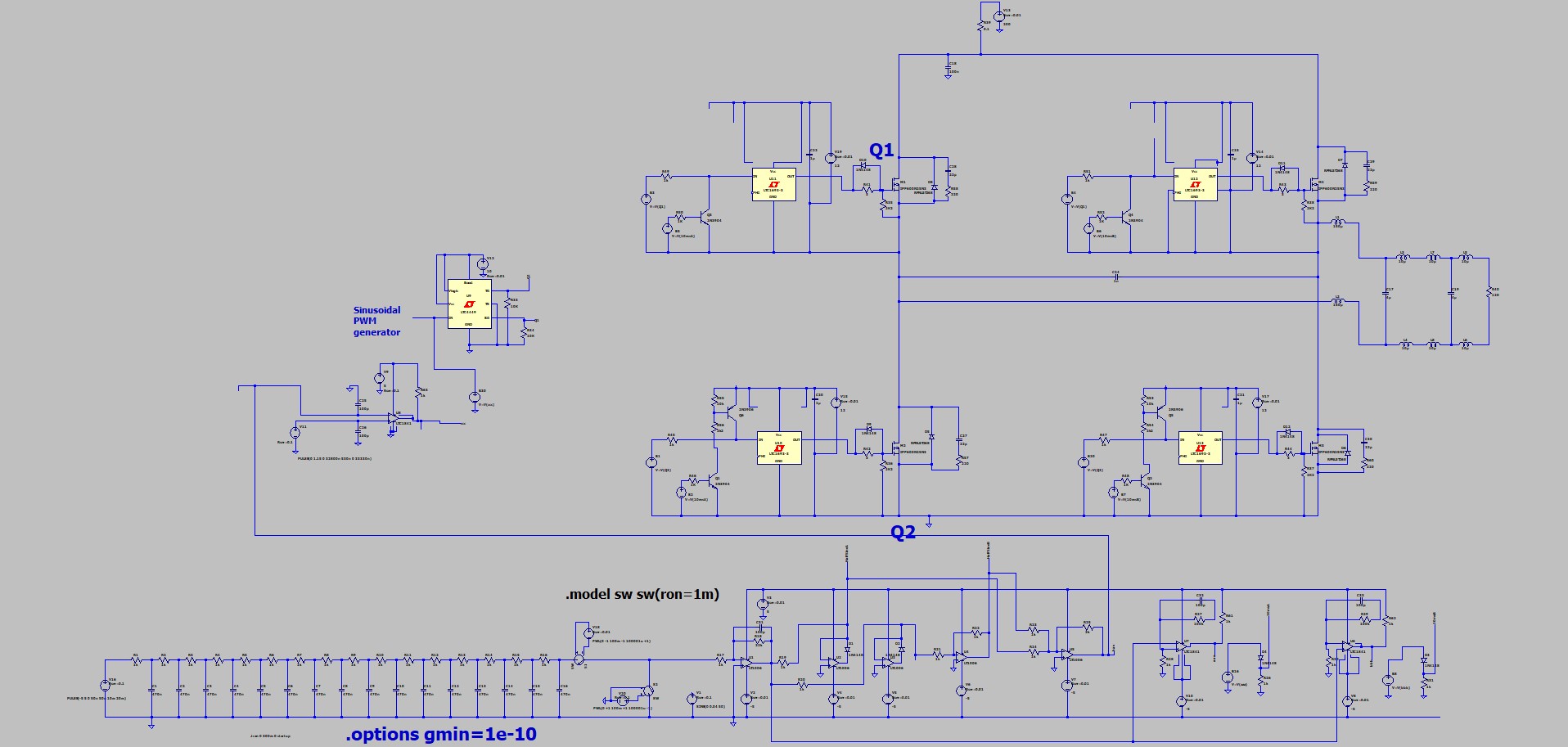

We are doing a non grid tied sinusoidal inverter.

VDC in = 190VDC, vac output = 110-126VAC.

As in the attached, the modus operandi is as follows...

1....For 10ms...Left leg FETs switch, and right leg top FET is OFF for the 10ms, and right leg bottom FET is ON for the 10ms

2....For 10ms...Right leg FETs switch, and Left leg top FET is OFF for the 10ms, and Left leg bottom FET is ON for the 10ms

....repeat above, etc etc

Is it possible to do a sinusoidal inverter, where the FETs switch together in diagonal pairs? (instead of same leg pairs)

We are doing a non grid tied sinusoidal inverter.

VDC in = 190VDC, vac output = 110-126VAC.

As in the attached, the modus operandi is as follows...

1....For 10ms...Left leg FETs switch, and right leg top FET is OFF for the 10ms, and right leg bottom FET is ON for the 10ms

2....For 10ms...Right leg FETs switch, and Left leg top FET is OFF for the 10ms, and Left leg bottom FET is ON for the 10ms

....repeat above, etc etc

Is it possible to do a sinusoidal inverter, where the FETs switch together in diagonal pairs? (instead of same leg pairs)