Jalpa Pandya

Newbie level 5

- Joined

- Jan 20, 2014

- Messages

- 10

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Activity points

- 59

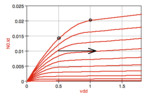

in the above circuit there are NMOS and PMOS Current mirror circuits. PMOS SW and NMOS SW blocks represent the mos switches. the W/L ratio for Current mirror circuit is 10/0.18um. the W/L ratio for switches are 2.3/0.18.

If the w/l ratio is increased then the output current provided by the current mirror circuit increases and vice versa. Currently i am getting o/p current of 80ua for reference current of 100ua.