graphene

Full Member level 2

- Joined

- Mar 22, 2012

- Messages

- 129

- Helped

- 4

- Reputation

- 8

- Reaction score

- 3

- Trophy points

- 1,298

- Location

- Germany

- Activity points

- 2,181

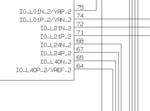

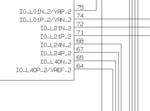

I now want to place the input/output signals perfectly into a particular pin as described in my circuit plan. I am using Spartan-3 XC3S400, XIlinx ISE 14.7. As shown in figures below, I need the pin 67, 65, 64 to be assigned for particular scalar ports.

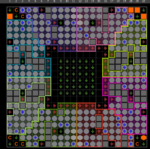

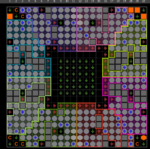

However, when I use my Planahead 14.7 is shows me a layout of IO planning but doesnt specify the pin numbers but rather shows them as W22, R1, C22, etc. In the IO planning layout I have A-Y, AA, AB in column and 1-22 in row. Now how do I find the pins 67, 65, 64 ? Any suggestions?

I have my VHDL FPGA design tested. I have also set timing constraints.

However, when I use my Planahead 14.7 is shows me a layout of IO planning but doesnt specify the pin numbers but rather shows them as W22, R1, C22, etc. In the IO planning layout I have A-Y, AA, AB in column and 1-22 in row. Now how do I find the pins 67, 65, 64 ? Any suggestions?

I have my VHDL FPGA design tested. I have also set timing constraints.