Eshal

Advanced Member level 1

- Joined

- Aug 29, 2012

- Messages

- 470

- Helped

- 16

- Reputation

- 32

- Reaction score

- 15

- Trophy points

- 1,298

- Location

- Nowhere :)

- Activity points

- 5,149

Hello experts!

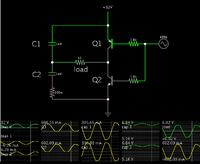

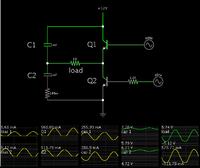

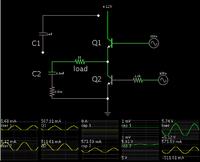

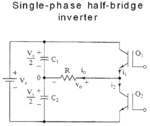

Here is the picture of Single phase half bridge inverter with R load only

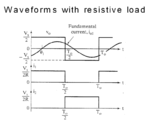

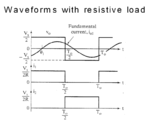

Here is waveforms with R load

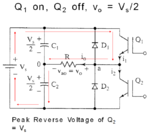

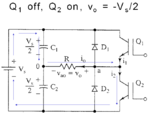

My task is to design this inverter with proper values of C and proper Transistors, initially by choosing any Vs value and R value.

So, what if I start my designing by choosing Vs=12v? And if I choose R=10ohm.

I am not going to design it for any hi-fi values. Just small values of Vs and R. So what should be those values?

Thanks experts.

Here is the picture of Single phase half bridge inverter with R load only

Here is waveforms with R load

My task is to design this inverter with proper values of C and proper Transistors, initially by choosing any Vs value and R value.

So, what if I start my designing by choosing Vs=12v? And if I choose R=10ohm.

I am not going to design it for any hi-fi values. Just small values of Vs and R. So what should be those values?

Thanks experts.