dominguesg

Newbie level 3

Hello Folks!

I'm trying to simulate a Full Bridge Inverter in PSpice using the HCPL-316j as the driver. I'm using bipolar SPWM, and a simple PWM circuit using AmpOp. The driver is switching the SIHG47N60E MOSFET from Vishay. I'm using the real models from MOSFET and Driver. The problem is: when I try to raise the Vsin (PWM Ref) peak value, 2 drivers start to switch with the two others, and consequently, shorting the MOSFET's. I really need the help of the community because this is my final project to graduate. I don't know what I'm doing wrong. The curves showing the problem folows below:

The circuit is structured on this way: PWM -> Dead Time ->Drivers(1,2,3,4) -> MOSFET's (1,2,3,4) -> LC Filter -> Rload

PWM Circuit:

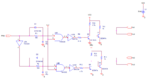

Dead Time Circuit

Driver:

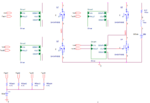

Full Bridge:

Filter:

This is the curves of input:

Here is the normal operation:

Here is one short in detail:

Every help is wanted! :razz:

Thanks!! :thumbsup:

I'm trying to simulate a Full Bridge Inverter in PSpice using the HCPL-316j as the driver. I'm using bipolar SPWM, and a simple PWM circuit using AmpOp. The driver is switching the SIHG47N60E MOSFET from Vishay. I'm using the real models from MOSFET and Driver. The problem is: when I try to raise the Vsin (PWM Ref) peak value, 2 drivers start to switch with the two others, and consequently, shorting the MOSFET's. I really need the help of the community because this is my final project to graduate. I don't know what I'm doing wrong. The curves showing the problem folows below:

The circuit is structured on this way: PWM -> Dead Time ->Drivers(1,2,3,4) -> MOSFET's (1,2,3,4) -> LC Filter -> Rload

PWM Circuit:

Dead Time Circuit

Driver:

Full Bridge:

Filter:

This is the curves of input:

Here is the normal operation:

Here is one short in detail:

Every help is wanted! :razz:

Thanks!! :thumbsup: