vsvamsi

Newbie level 4

- Joined

- Apr 2, 2013

- Messages

- 5

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,316

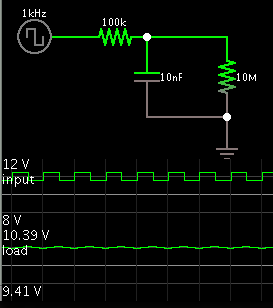

I have a montonicity issue with my DAC with worst case DNL during transition from 0111 1111 to 1000 000. There is a massive glitch during this transition. the output impedance of current source I designed is very high 10Mohms. I have noticed the glitches in certain bits from the D flip flop outputs which inputs the signal to the switches of the current source. I have tested the thermometer decoder,It is working great.

Can u tell me what i should do to rectify this error. I have been working on it for long time.

Can u tell me what i should do to rectify this error. I have been working on it for long time.