Andrea Scafuto

Newbie level 4

- Joined

- Nov 2, 2013

- Messages

- 7

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Activity points

- 63

Hello gurus, i'm new at VHDL programming, i have to create a Scan Chain from scratch, and starting from this one i have to test a Component.

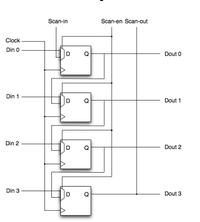

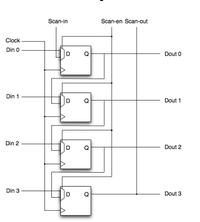

I created first of all flip-mux, a component that combine a D-latch flip flop and 2-1 Multipliplexer.

My scanchain is composed by 4 flip-mux, when Scan_en is disabled, the scan chain output is the input Din0, Din1,Din2, Din3.

I implemented my scanchain, I need to create the "Component".

I was thinking a simple 1 bit adder, for example:

if the output string is -> 0 0 1 0

after the string goes into the Component the exit will be -> 0 0 1 1

To implement this i've created a new vhdl module that has 4 input and 4 output, now how i can handle the scope of my scanchain variables, to implement my component?

I created first of all flip-mux, a component that combine a D-latch flip flop and 2-1 Multipliplexer.

My scanchain is composed by 4 flip-mux, when Scan_en is disabled, the scan chain output is the input Din0, Din1,Din2, Din3.

I implemented my scanchain, I need to create the "Component".

I was thinking a simple 1 bit adder, for example:

if the output string is -> 0 0 1 0

after the string goes into the Component the exit will be -> 0 0 1 1

To implement this i've created a new vhdl module that has 4 input and 4 output, now how i can handle the scope of my scanchain variables, to implement my component?