qasheef

Newbie

Hi

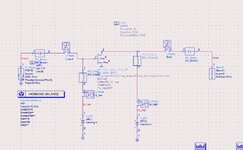

I am designing an X band amplifier using Win PDK MMIC kit.

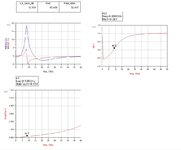

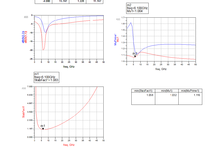

During initial analysis, with 50 ohm terminations at input and output port, the amplifier S(1,1) and S(2,2) are negative.

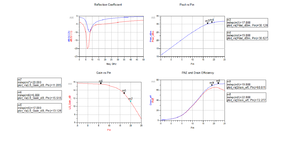

As a first step, i did load/ source pull using ADS built in template and get the Zs / Zl source and load impedances for max PAE. Then I inserted ZL as load impedance and conjugate of Zs as source impedance in ideal circuit, but the S(1,1) and S(2,2) becomes positive at frequencies from 1 to 8 GHz.

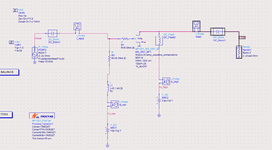

I have to add a resistor of around 24 ohm to make S(1,1) and S(2,2) lower than zero. But in this case, i am unable to get the performance from the transistor.

I am confused how to go about with the design. Should i first stablize the transistor and then go for design, for i should do the stability check at the end after making input / output matching network.

What can be the possible reason of having positive return loss in my design.

I tried to stabilize my transistor using a parallel RC network, however, the affect of Capacitance is negilible on the stability.

I am stuck how should i go forward with the design

I am designing an X band amplifier using Win PDK MMIC kit.

During initial analysis, with 50 ohm terminations at input and output port, the amplifier S(1,1) and S(2,2) are negative.

As a first step, i did load/ source pull using ADS built in template and get the Zs / Zl source and load impedances for max PAE. Then I inserted ZL as load impedance and conjugate of Zs as source impedance in ideal circuit, but the S(1,1) and S(2,2) becomes positive at frequencies from 1 to 8 GHz.

I have to add a resistor of around 24 ohm to make S(1,1) and S(2,2) lower than zero. But in this case, i am unable to get the performance from the transistor.

I am confused how to go about with the design. Should i first stablize the transistor and then go for design, for i should do the stability check at the end after making input / output matching network.

What can be the possible reason of having positive return loss in my design.

I tried to stabilize my transistor using a parallel RC network, however, the affect of Capacitance is negilible on the stability.

I am stuck how should i go forward with the design