arya.jagadeesh

Member level 2

- Joined

- Jul 16, 2013

- Messages

- 44

- Helped

- 4

- Reputation

- 8

- Reaction score

- 4

- Trophy points

- 8

- Location

- INDIA

- Activity points

- 285

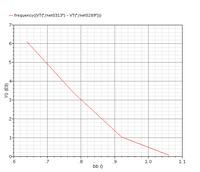

in ring oscillator using cmos inverter if i wanted to increase the frequency.....i have to charge and discharge the capacitor faster ...so i wanted to increase the current ...by incresing width of transistor but this will work upto certain point......is there any other way to increase the current