shauns87

Junior Member level 1

Hi,

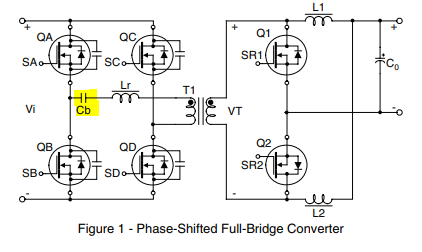

Under which design conditions, we need to add the series resonant capacitor in phase shifted full bridge converters? "Cb" marked in yellow in the image below:

t

t

There are many reference designs which doesn't have additional resonant capacitor but only resonant inductor if the leakage inductance is not enough in the main transformer. However, I am unsure if we really to add the resonant capacitor as well. As per one of the application notes from Vishay - "It isnecessary to add Cb to avoid an unbalance of thetransformer flux and saturation of the transformer". However, it is not clear to me. Also, I am unsure how I can calculate the value of Cb if I have to use it in the design.

By any chance, can I get some help behind the theory or if there is any resource available to read to get more insight on this topic.

Thanks.

Under which design conditions, we need to add the series resonant capacitor in phase shifted full bridge converters? "Cb" marked in yellow in the image below:

There are many reference designs which doesn't have additional resonant capacitor but only resonant inductor if the leakage inductance is not enough in the main transformer. However, I am unsure if we really to add the resonant capacitor as well. As per one of the application notes from Vishay - "It isnecessary to add Cb to avoid an unbalance of thetransformer flux and saturation of the transformer". However, it is not clear to me. Also, I am unsure how I can calculate the value of Cb if I have to use it in the design.

By any chance, can I get some help behind the theory or if there is any resource available to read to get more insight on this topic.

Thanks.