Bruno5234

Newbie level 5

Hi, I designed a buck converter that powers a push pull inverter that I designed too, I want to control the voltage in the buck converter while powering the inverter, the problem I'm facing is that I can control de voltage in the buck converter pretty easy when putting a resistor load, but when I connect the inverter as a load (with a resistor load at the secondary of the inverter's transformer) I can see some high frequency noise at the output of the buck converter and I want to reduced it because I don't want to damage my microcontroller and I'm also getting a bad voltage reading because of this noise, I tried increasing the size of the bulk capacitor of the buck converter and that decreased the amplitude of the noise but made my control system slower, so I think that is not the way to solve the problem. Any ideas?

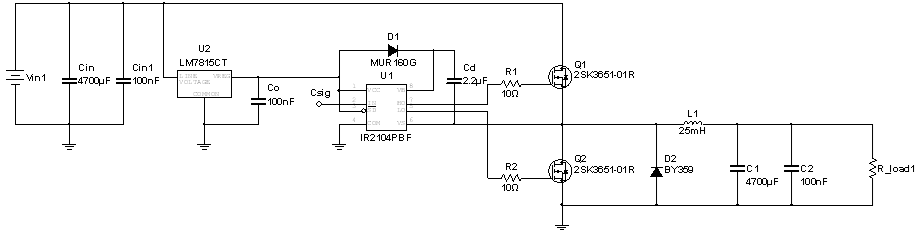

This is the schematic of my circuit:

Buck converter:

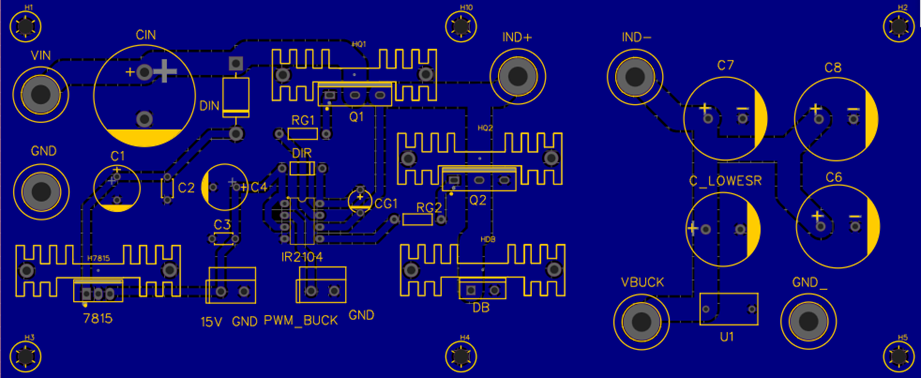

And this is the PCB I designed:

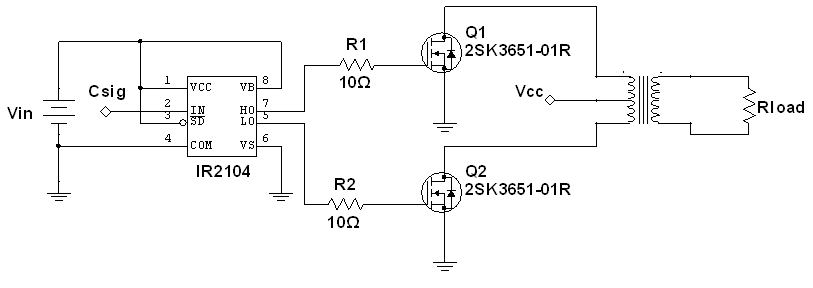

Push Pull Inverter circuit:

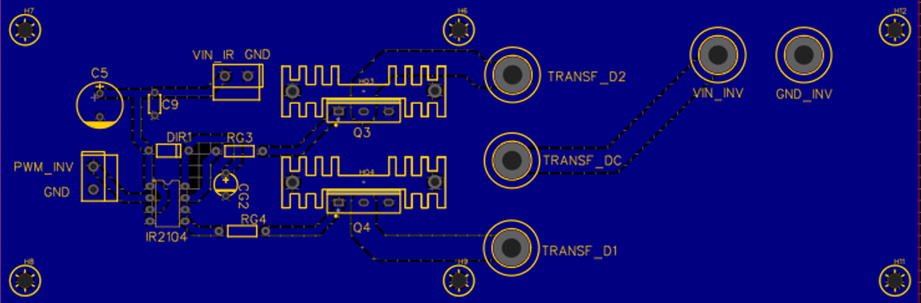

Push Pull Inverter PCB

I don't know a lot about PCB design so I probably made a mistake with the design

The Buck converter is control by a PWM of 32 kHz frequency, the push pull inverter is working with 200 kHz of frequency

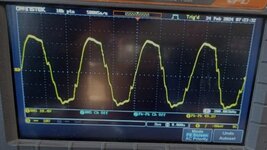

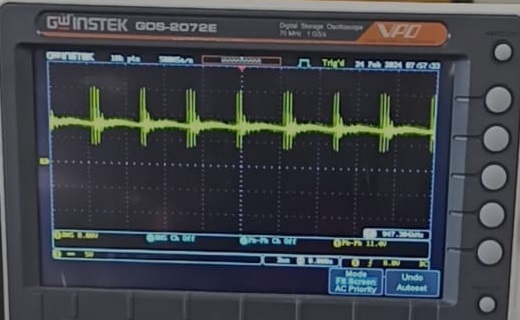

The noise I'm getting is this:

The frequency of the noise is the double the frequency of the inverter, so I think the problem has to be the inverter

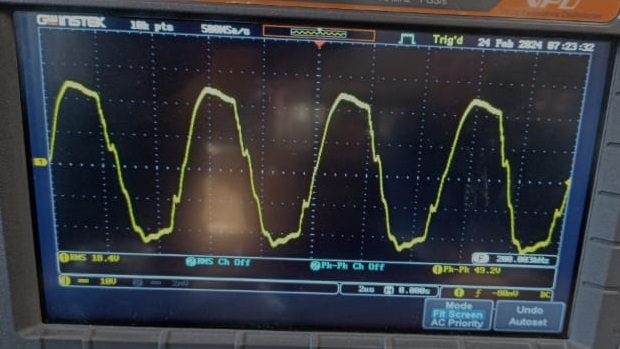

I don't know if this provide some extra information but this is the waveform I get at the secondary of the inverter

The transformer I'm using for the inverter is a toroidal transformer designed for the frequency of the inverter

Please let me know if you need extra information

Thank you for answering

This is the schematic of my circuit:

Buck converter:

And this is the PCB I designed:

Push Pull Inverter circuit:

Push Pull Inverter PCB

I don't know a lot about PCB design so I probably made a mistake with the design

The Buck converter is control by a PWM of 32 kHz frequency, the push pull inverter is working with 200 kHz of frequency

The noise I'm getting is this:

The frequency of the noise is the double the frequency of the inverter, so I think the problem has to be the inverter

I don't know if this provide some extra information but this is the waveform I get at the secondary of the inverter

The transformer I'm using for the inverter is a toroidal transformer designed for the frequency of the inverter

Please let me know if you need extra information

Thank you for answering