BlackHelicopter

Full Member level 2

Not even sure how to ask this or why I can't seem to wrap my head around it.

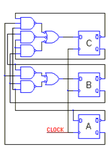

When exchanging data between registers, as in the example state machine attached, how do the 'Q' outputs stay stable between state changes? For instance at the active edge of the clock, the data at the 'D' inputs are clocked into the register, therefore causing a change at the 'Q' outputs. Well since since the 'Q' outputs are fed back into the 'D' inputs how does data stay stable long enough to satisfy the setup and hold time of the inputs to the registers. Lets say for instance, a state change occurs, the data is clocked into the registers at the rising edge of the clock, and after some propagation delay (after the rising edge of the clock) the 'Q' outputs change, now what if the output of one of the registers changes fast enough that its faster than the hold time of an input to a different register, what happens then? or is that not even possible?

This question also came about when I was reading a chapter in a book (see attachments 2&3). The authors describes creating a data path using two registers which is used to add up the factorial of a value, there are two registers one for the counter and one for the sum. Well the author goes on to define the control word table, and then he then simplifies it a bit by combining two operations: the load of the 'product' register and the 'down count' of the counter. My question is, at the rising edge of the clock, the 'down counter' is going to count down and the 'product' is going to load the old previous product (which is derived from the output of the counter), what's to keep the output of the counter register from changing sooner than the hold time of the 'product' register and screwing up its value.

Does anyone understand what I'm trying to say?

When exchanging data between registers, as in the example state machine attached, how do the 'Q' outputs stay stable between state changes? For instance at the active edge of the clock, the data at the 'D' inputs are clocked into the register, therefore causing a change at the 'Q' outputs. Well since since the 'Q' outputs are fed back into the 'D' inputs how does data stay stable long enough to satisfy the setup and hold time of the inputs to the registers. Lets say for instance, a state change occurs, the data is clocked into the registers at the rising edge of the clock, and after some propagation delay (after the rising edge of the clock) the 'Q' outputs change, now what if the output of one of the registers changes fast enough that its faster than the hold time of an input to a different register, what happens then? or is that not even possible?

This question also came about when I was reading a chapter in a book (see attachments 2&3). The authors describes creating a data path using two registers which is used to add up the factorial of a value, there are two registers one for the counter and one for the sum. Well the author goes on to define the control word table, and then he then simplifies it a bit by combining two operations: the load of the 'product' register and the 'down count' of the counter. My question is, at the rising edge of the clock, the 'down counter' is going to count down and the 'product' is going to load the old previous product (which is derived from the output of the counter), what's to keep the output of the counter register from changing sooner than the hold time of the 'product' register and screwing up its value.

Does anyone understand what I'm trying to say?