kenambo

Full Member level 6

Hi all

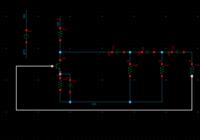

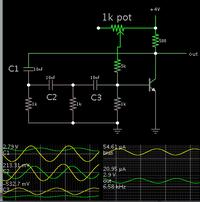

I am using 40nm PDK and i want to implement a RC oscillator of 1MHz using given npn pdk transistor.

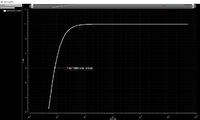

while setting Q-point i got that my transitor BW is ft = 2.7MHz.

and my supply voltage is 1.1V.

i am using conventional design of RC oscillator.

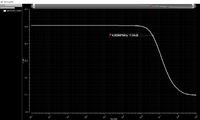

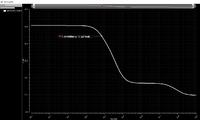

But my circuit doesn't start oscillatons. I dont know whether it is my initial conditions problem or circuit problem.

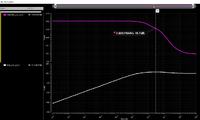

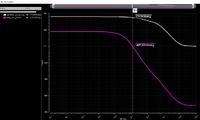

and i heard that for oscillator analysis HB simulation is better than transcient simulation. Is it true?

If so, how can i implement it in cadence?

please help..

thanks.

I am using 40nm PDK and i want to implement a RC oscillator of 1MHz using given npn pdk transistor.

while setting Q-point i got that my transitor BW is ft = 2.7MHz.

and my supply voltage is 1.1V.

i am using conventional design of RC oscillator.

But my circuit doesn't start oscillatons. I dont know whether it is my initial conditions problem or circuit problem.

and i heard that for oscillator analysis HB simulation is better than transcient simulation. Is it true?

If so, how can i implement it in cadence?

please help..

thanks.