frankrose

Advanced Member level 3

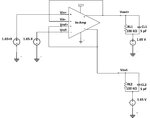

I would like to see your simulation settings, the DC sources, internal and external device values, parameter settings, etc. I understand you tried to simulate that circuit, but the figure is not same as the test schematic with the elements in Cadence. For example how much are the feedback resistors? It is not added to the figure, but if they too low the gain can drop and output stage can leave the normal active region.i didnt share the circuit not because i dont want to share it, but because i am not in the city of my university, however the setup from the gray is exactly the same setup i am performing, i am applying differential input voltage and sweeping it and getting the output.

And which is exactly in triode? Figure doesn't show it.for sure at the non linear part of my graph some of them will be triode

No. For every DC operating point, so for every DC input and output values the circuit has different small-signal model. This small-signal model can tell you how much is the DC gain too, not just the high-frequency gain. Think about Bode plot, which is an AC characteristic, but left side of the characteristic is basically the DC gain value, which is the loop gain's maximum value! Thus, if your amplifier devices are in triode region the gain from DC simulation and the maximum open-loop gain from AC simulation will decrease too.the non linearity you mentioned about with decreasing the loop gain is not the case of my situation since I am running dc simulation where the gain is highest, that what you talk about is when applying an ac signal with high frequency.

And how does it look like in Cadence? Are you using ideal devices? How the CMFB of this last circuit looks like? Many details are missing.but sine you you know the idea is from gray i can tell you that i did exactly as same he did in this picture but for my folded amp