diarmuid

Full Member level 2

- Joined

- Aug 4, 2011

- Messages

- 143

- Helped

- 10

- Reputation

- 20

- Reaction score

- 9

- Trophy points

- 1,308

- Location

- Dublin, Ireland

- Activity points

- 2,429

Hello,

I need to design a 7bit R2R current DAC.

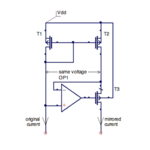

I am looking at the current mode R2R DAC architecture as a basis. However, I do not

want to convert the output currents to a voltage. I simply want to mirror them out.

This means I wont use an opamp at the output. I am finding this leaves me with the

situation where the reference and output nets at the base of my DAC are not always

at the same voltage, thus messing up my R-2R ratios.

Does anyone have any idea of how to overcome this, good reading material, etc.?

At the end of the day all I want is a DAC whereby my binary weighted currents are mirrored

to elsewhere in the circuit. I want also to avoid the more conventional binary weighted unit

FET approach.

Thanks,

Diarmuid

I need to design a 7bit R2R current DAC.

I am looking at the current mode R2R DAC architecture as a basis. However, I do not

want to convert the output currents to a voltage. I simply want to mirror them out.

This means I wont use an opamp at the output. I am finding this leaves me with the

situation where the reference and output nets at the base of my DAC are not always

at the same voltage, thus messing up my R-2R ratios.

Does anyone have any idea of how to overcome this, good reading material, etc.?

At the end of the day all I want is a DAC whereby my binary weighted currents are mirrored

to elsewhere in the circuit. I want also to avoid the more conventional binary weighted unit

FET approach.

Thanks,

Diarmuid