yefj

Advanced Member level 4

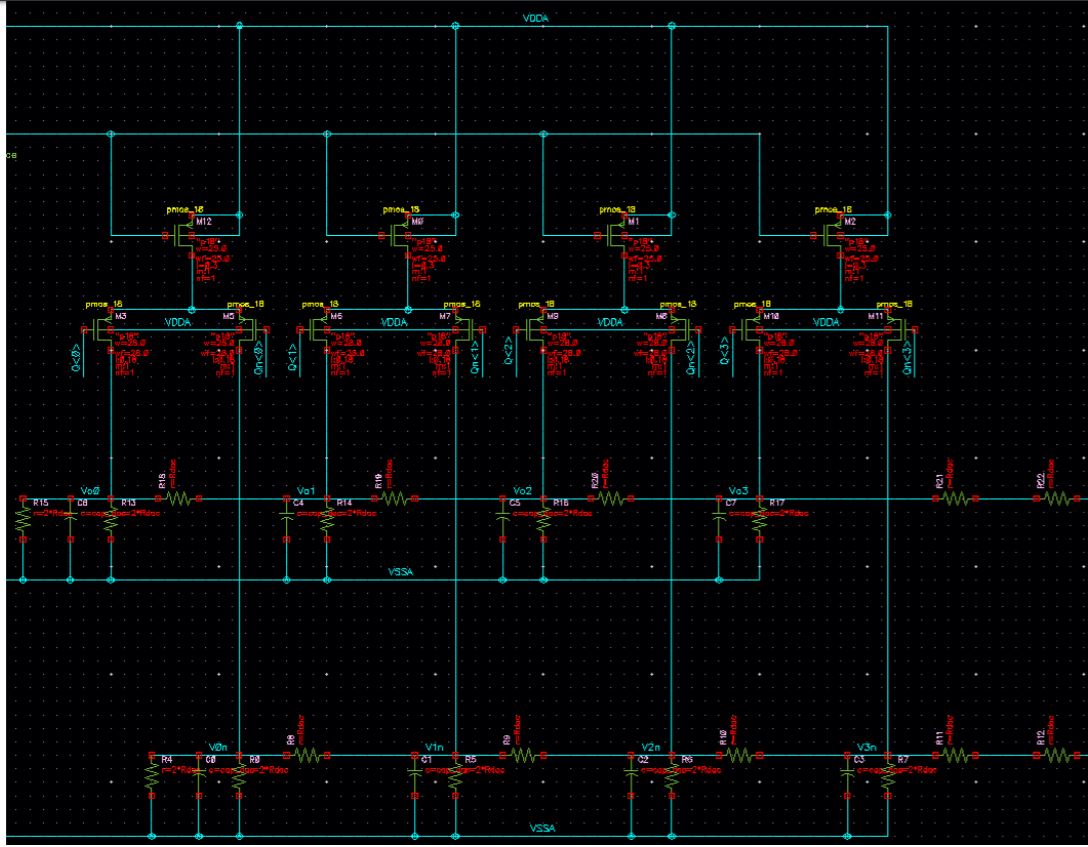

Hello, in the photo bellow i have a partial photo of analog implementation of a R 2R DAC.

However there is no exaplanation regarding why we need those lines of parallel capacitances and resistors.

I cant see where i connect the OPAMPS even.

I couldnt find this exact R-2R DAC there are many types.

If someone recognises this circuit configuration could you please post an article regarding such configuration?

Thanks.

However there is no exaplanation regarding why we need those lines of parallel capacitances and resistors.

I cant see where i connect the OPAMPS even.

I couldnt find this exact R-2R DAC there are many types.

If someone recognises this circuit configuration could you please post an article regarding such configuration?

Thanks.