liubangan

Newbie

- Joined

- Apr 24, 2011

- Messages

- 1

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,292

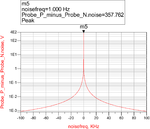

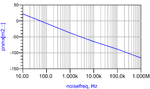

Hi, everyone. I'm designing a LC cross-coupled oscillator using TSMC 65nm CMOS process. I have simulated the circuit using harmonic balance simulator in ADS. One of the problems I encountered is that the simulation give extremely high phase noise results. In fact, the phase noise is larger than the output signal. I was wondering if I have missed some settings at first, but after I studied some examples provided by Agilent, I found the similar problems in examples\RFIC\MOS_VCO_wrk, the graph is in VCO_wVaractors.dds. Following are the graphs, the first two are simulation results of mine, the third one is graph from the example.