nervecell_23

Member level 1

- Joined

- Apr 26, 2013

- Messages

- 38

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,286

- Activity points

- 1,565

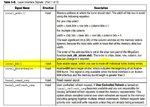

I want to write to a DDR2 RAM from a custom architecture. The RAM has 64bits data width and runs at 400MHz. The custom architecture is interfering with the memory controller by using Avalon-MM interface. The memory controller is set to half-rate mode which means local data width is 256bits and one word on local side is equal to 4 words on memory side (4*8byte aligned).

My question is if I just want to write a 64bits word to the memory without damaging other content in it, is there anyway to do that (such as write byte-enable signal)? Since if I write a 256bits word to the memory with only 64bits that are meaningful, the other 192 dummy bits is going to replace the original content in the memory right?

My question is if I just want to write a 64bits word to the memory without damaging other content in it, is there anyway to do that (such as write byte-enable signal)? Since if I write a 256bits word to the memory with only 64bits that are meaningful, the other 192 dummy bits is going to replace the original content in the memory right?