Hawaslsh

Full Member level 3

- Joined

- Mar 13, 2015

- Messages

- 164

- Helped

- 5

- Reputation

- 10

- Reaction score

- 7

- Trophy points

- 1,298

- Location

- Washington DC, USA

- Activity points

- 3,422

Hello,

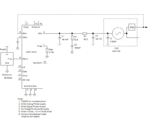

We are working with a VCO and made a PLL work fairly well and cheaply on the bench, but in trying to transition to a stand alone device we ran into a problem. The block diagram is above, a mixer is used to downconvert the divide by 16 output of the VCO to a known reference (~ 1 MHz). The phase frequency detector (PFD) in the CD4046 is TTL, but the mixer output is AC coupled, so an op-amp is used to add a DC offset.

A large caveat to the whole thing, and the roof of the problem, for the VCO N/16 output to come near the 1.5 GHz reference, the Vcont on the VCO needs to be ~2.3V. Anything ± .4V and the frequency of the downconverted signal becomes too high for the op-amp and PFD. So, in order to "jump start" the loop we used a triple power supply (BK 1651). We set the +24V output to independent, and once the VCO output approached the reference, and the downconverted signal was below 32ish MHz, the loop took over.

In trying to move away from the bench, we tried the same idea with a voltage divider, but the lock was super unstable. Looking back on it, I'm not even sure why it worked attached to the power supply, I assume the output should have been regulated? There is a better way to solve this problem? Self admittedly, I know only what i've read about PLLs in the past month or so... so, not much.

Any insights would be appreciated.

We are working with a VCO and made a PLL work fairly well and cheaply on the bench, but in trying to transition to a stand alone device we ran into a problem. The block diagram is above, a mixer is used to downconvert the divide by 16 output of the VCO to a known reference (~ 1 MHz). The phase frequency detector (PFD) in the CD4046 is TTL, but the mixer output is AC coupled, so an op-amp is used to add a DC offset.

A large caveat to the whole thing, and the roof of the problem, for the VCO N/16 output to come near the 1.5 GHz reference, the Vcont on the VCO needs to be ~2.3V. Anything ± .4V and the frequency of the downconverted signal becomes too high for the op-amp and PFD. So, in order to "jump start" the loop we used a triple power supply (BK 1651). We set the +24V output to independent, and once the VCO output approached the reference, and the downconverted signal was below 32ish MHz, the loop took over.

In trying to move away from the bench, we tried the same idea with a voltage divider, but the lock was super unstable. Looking back on it, I'm not even sure why it worked attached to the power supply, I assume the output should have been regulated? There is a better way to solve this problem? Self admittedly, I know only what i've read about PLLs in the past month or so... so, not much.

Any insights would be appreciated.