hassan590

Newbie level 3

- Joined

- Sep 17, 2013

- Messages

- 3

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Activity points

- 37

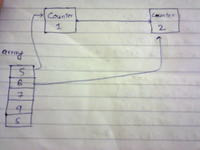

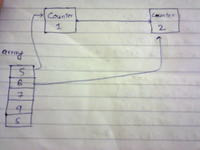

I am a beginner in vhdl. i just learned how do we program in vhdl. i was trying to make a program which has two entities as counters i declared an array and different values are placed at each location in that array. the counter has to pick a value from each location and decrements it down to zero i want both counters to pick values from the same array in such away that 1st counter picks value from 1st location and 2nd counter from second counter picks from second location the one who decrements to zero first, picks the value from next location. My supervisor gave me this task to understand how to entities interact with each other. I need some help to complete that task. i have written code for one counter which is decrementing the values after picking them from array and i have no idea how 2nd counter would be working with counter 1 to perform the actual task which is mentioned above.what should i be doing? i hope u people would help me.

Code VHDL - [expand]

Last edited by a moderator: