sawakita

Newbie level 5

- Joined

- May 14, 2013

- Messages

- 8

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,374

Hi good day,

If someone could please explain to me this circuitry working principle. I have search many books and articles but havent really find any answer to my question.

I understand how the bandgap reference circuit works and the principle. I can understand the typical bandgap reference circuit.

But I have problem where there's a cross couple circuitry involves.

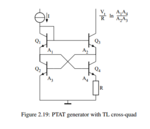

based on the picture attached,

I dont understand how the currents flows in this circuitry especially at the cross coupled based.

I understand the current mirror on top and that both currents flows at Q3 and Q1,

my question is let say Q4 is off, so current from Q3 flows to base of Q2 turning on Q2,

that means current from Q1 is shorted to ground when Q2 is turned on.

that means currents from Q1 would never flows to base of Q4 because Q2 is always on due to Q4 always off.

so in this case how does Q4 activate?

to generate PTAT both Q2 and Q4 needs to turn on to get the delta_vbe.

I have search in this threads the answer but couldnt find any.

Thanks in advance for the explaination.