esteemera

Newbie level 2

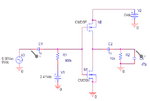

In the attachment, capacitors and high value resistors have been used. What is the purpose? Is it to minimize distortion and maintain the stability in the mid frequency band?

I don't have software's to try simulate and check the result. Any thoughts on the output of the amplifier for different resistor or capacitor values?

Thanks.