jcu85

Newbie

Hello All,

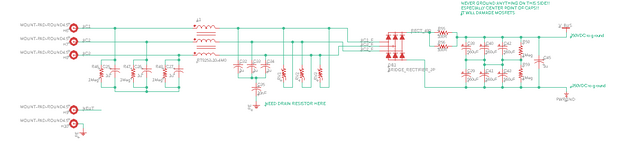

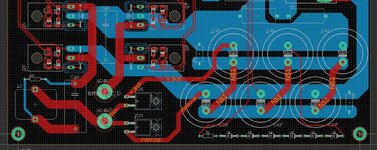

To begin, I am designing a ~3kW phase shifted full bridge design, to take 250VDC to ~1200VDC at ~2.5A. All component selection was based on TI's UCC2895 datasheet.

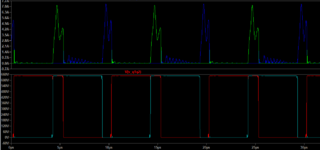

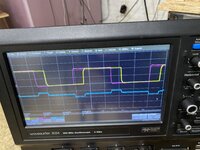

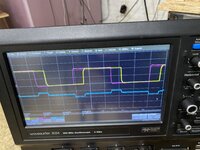

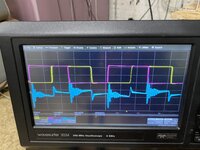

I am experiencing an oscillation in primary current when running the output of my transformer into a rectification stage. When running the mosfet power stage into a resistive load, of a similar power draw, I am not experiencing any oscillation of current. Likewise, when running the mosfet power stage into the transformer, then directly into a resistive load, there are little to no oscillations. My problem only exists while I am running into the rectification stage.

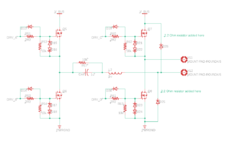

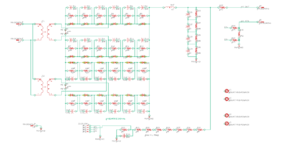

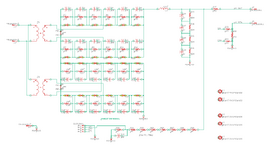

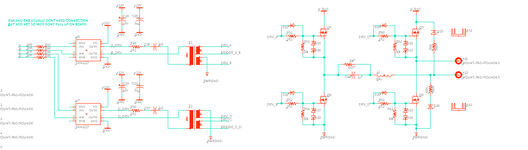

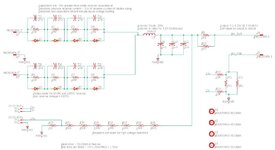

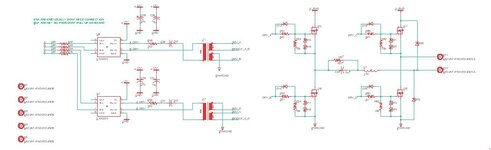

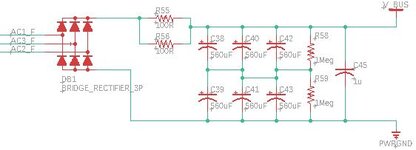

I have attached a picture of the rectification stage to this post - I have since removed the capacitors parallel to the diodes, since I believe my problem to be related to leakage inductance and capacitance on the secondary. I have additionally attached an excerpt of the power stage, as well as scope shots of the bridge current running into a resistive load and into the rectification stage.

I have read through the "Phase Shift Full Bridge SMPS is massively over-hyped" thread, originally posted by treez. One important thing I noticed, is Easy Peasy's suggestion to incorporate a 1nF across the mosfets in the power stage, which I will work to test tomorrow.

I have seen additional designs in which there is an RCD snubber on the output of the rectifier diodes, before the series inductance. I will have to run simulation to find a design that is appropriate.

Aside from these points, is there anything missing I could try?

Thank you

To begin, I am designing a ~3kW phase shifted full bridge design, to take 250VDC to ~1200VDC at ~2.5A. All component selection was based on TI's UCC2895 datasheet.

I am experiencing an oscillation in primary current when running the output of my transformer into a rectification stage. When running the mosfet power stage into a resistive load, of a similar power draw, I am not experiencing any oscillation of current. Likewise, when running the mosfet power stage into the transformer, then directly into a resistive load, there are little to no oscillations. My problem only exists while I am running into the rectification stage.

I have attached a picture of the rectification stage to this post - I have since removed the capacitors parallel to the diodes, since I believe my problem to be related to leakage inductance and capacitance on the secondary. I have additionally attached an excerpt of the power stage, as well as scope shots of the bridge current running into a resistive load and into the rectification stage.

I have read through the "Phase Shift Full Bridge SMPS is massively over-hyped" thread, originally posted by treez. One important thing I noticed, is Easy Peasy's suggestion to incorporate a 1nF across the mosfets in the power stage, which I will work to test tomorrow.

I have seen additional designs in which there is an RCD snubber on the output of the rectifier diodes, before the series inductance. I will have to run simulation to find a design that is appropriate.

Aside from these points, is there anything missing I could try?

Thank you

Attachments

-

Driver_stage_into_Rectification_stage.JPG4.1 MB · Views: 177

Driver_stage_into_Rectification_stage.JPG4.1 MB · Views: 177 -

Driver_stage_into_load.JPG4.1 MB · Views: 145

Driver_stage_into_load.JPG4.1 MB · Views: 145 -

Driver_stage_into_load.JPG4.1 MB · Views: 128

Driver_stage_into_load.JPG4.1 MB · Views: 128 -

Driver_stage_into_Rectification_stage.JPG4.1 MB · Views: 160

Driver_stage_into_Rectification_stage.JPG4.1 MB · Views: 160 -

1200V_Rectifier_Stage.JPG76.2 KB · Views: 168

1200V_Rectifier_Stage.JPG76.2 KB · Views: 168 -

1200V_Power_Stage.JPG44.2 KB · Views: 170

1200V_Power_Stage.JPG44.2 KB · Views: 170 -

1671486790347.png43.7 KB · Views: 189

1671486790347.png43.7 KB · Views: 189

![IMG_5214[1].JPG](/data/attachments/110/110340-4af3d22d4e43378f278e600e9cc84cb5.jpg)

![IMG_5215[1].JPG](/data/attachments/110/110342-92cfd53e3cac5e0176bf45126d10db0a.jpg)