czq1419

Junior Member level 1

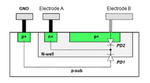

Hello, I'm doing the doing the pixel photodiode layout for the first time. It's a pinned-photodiode(p-sub/n-well/p+)

Should I fully cover the n-well region by ACT(active region) in layout? There are DRC and LVS errors if I do this, and if I only cover the p+ region(enclosed by n-well) with ACT, then DRC and LVS is OK but non-ACT regions will become STI in the photodiode which is not expected.

Anyone who has an idea? or other advice on this layout? Thanks alot!

DRC error:

1. ACT must be fully covered by NPLUS or PPLUS

LVS error:

1. The 2 contacts (one from p+ and the other from n+ in n-well) is regarded as shorted because they are located in the same ACT.

(BUT I'm using large ACT region only to define a non-STI region for photodiode, and from the cross-section, they shouldn't be shorted at all)

Should I fully cover the n-well region by ACT(active region) in layout? There are DRC and LVS errors if I do this, and if I only cover the p+ region(enclosed by n-well) with ACT, then DRC and LVS is OK but non-ACT regions will become STI in the photodiode which is not expected.

Anyone who has an idea? or other advice on this layout? Thanks alot!

DRC error:

1. ACT must be fully covered by NPLUS or PPLUS

LVS error:

1. The 2 contacts (one from p+ and the other from n+ in n-well) is regarded as shorted because they are located in the same ACT.

(BUT I'm using large ACT region only to define a non-STI region for photodiode, and from the cross-section, they shouldn't be shorted at all)