ahmad1954

Full Member level 4

I want to calculate linear range of a simple mos differential pair with hspice. this is my netlist:

Vdc1 1 6 0

vcm 6 0 3

VCC 11 0 DC 5

VDD 12 0 DC -5

M1 3 1 5 5 NMOS1 w=10u l=.1u

M2 4 6 5 5 NMOS1 w=10u l=.1u

RC1 11 3 1k

RC2 11 4 1k

RE 5 12 7.2K

.MODEL NMOS1 Nmos level=2

.print dc id(m1) id(m2)

.dc vdc1 -3 3 1m

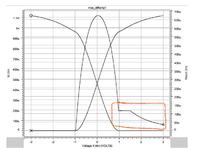

and this is output:

my question is why 2 graphs are not symmetric?

Vdc1 1 6 0

vcm 6 0 3

VCC 11 0 DC 5

VDD 12 0 DC -5

M1 3 1 5 5 NMOS1 w=10u l=.1u

M2 4 6 5 5 NMOS1 w=10u l=.1u

RC1 11 3 1k

RC2 11 4 1k

RE 5 12 7.2K

.MODEL NMOS1 Nmos level=2

.print dc id(m1) id(m2)

.dc vdc1 -3 3 1m

and this is output:

my question is why 2 graphs are not symmetric?