Yassir_eldo

Junior Member level 2

- Joined

- Mar 22, 2013

- Messages

- 21

- Helped

- 1

- Reputation

- 2

- Reaction score

- 1

- Trophy points

- 1,283

- Activity points

- 1,418

Hello everybody,

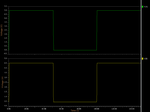

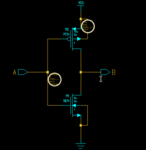

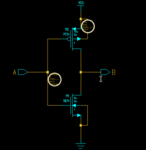

I am trying to simulate a CMOS inverter with transient analysis using BSIM4 Berkley Model in ELDO, but the simulation result that I found is a Follower (nearly the same curve than the input). Could anybody tell me why I have this problem with BSIM4v4? I have tried BSIM3v3, some TSMC models, BSIMSOI and I have all the time the inversion result. U find enclosed the schematic that I use.

Best regards

I am trying to simulate a CMOS inverter with transient analysis using BSIM4 Berkley Model in ELDO, but the simulation result that I found is a Follower (nearly the same curve than the input). Could anybody tell me why I have this problem with BSIM4v4? I have tried BSIM3v3, some TSMC models, BSIMSOI and I have all the time the inversion result. U find enclosed the schematic that I use.

Best regards