natnoraa

Full Member level 1

- Joined

- Jun 19, 2011

- Messages

- 98

- Helped

- 12

- Reputation

- 24

- Reaction score

- 11

- Trophy points

- 1,288

- Activity points

- 2,108

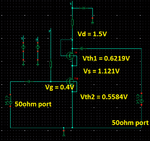

Possibility of a Class C Cascode power amplifier

Hi,

Would like some advice on a cascode Class C power amplifier. Having ran simulations for a couple of days, I am unable to successfully simulate a cascode Class C Power Amplifier. I would like the bottom transistor to operate as a true class C with Vg < Vth while the top transistor operating at saturation with Vds > Vgs -Vth. However, no matter how I bias the Vg of the top transistor, it's always in triode region. Does anyone know of any way or the possibility of this?

Natnoraa

Hi,

Would like some advice on a cascode Class C power amplifier. Having ran simulations for a couple of days, I am unable to successfully simulate a cascode Class C Power Amplifier. I would like the bottom transistor to operate as a true class C with Vg < Vth while the top transistor operating at saturation with Vds > Vgs -Vth. However, no matter how I bias the Vg of the top transistor, it's always in triode region. Does anyone know of any way or the possibility of this?

Natnoraa