sharankumargoud

Newbie level 6

- Joined

- Jan 30, 2013

- Messages

- 11

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,340

HI all

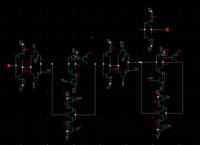

Can u guys please help me about the working and schematic of the pos edge async dff with active low set.

I am bit confused . Thanks in advanced

Can u guys please help me about the working and schematic of the pos edge async dff with active low set.

I am bit confused . Thanks in advanced