kishore680

Member level 5

- Joined

- Mar 14, 2012

- Messages

- 81

- Helped

- 3

- Reputation

- 6

- Reaction score

- 4

- Trophy points

- 1,298

- Location

- Bangalore

- Activity points

- 1,833

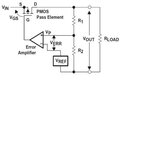

What should be the pass transistor design for optimum design. The Mos should be in CG state or CS or CD. Usually PMOS will be used in CG form .WHat happens if we use in CG or CDhttps://www.circuitstoday.com/wp-content/uploads/2011/06/LDO-regulator-schematic.png.