abhijitdutta2005

Newbie

- Joined

- Apr 6, 2013

- Messages

- 4

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,322

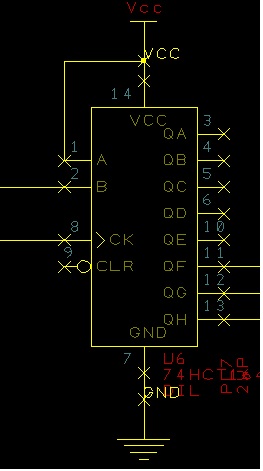

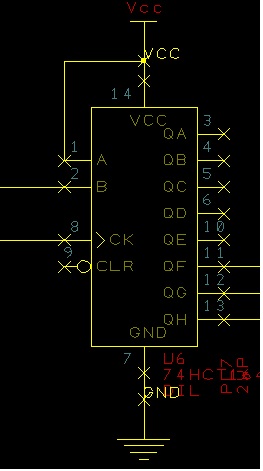

I have a circuit (+5V) where a 74HC164 input pin-2 is driven by the output of a 74ACT74/74ls74.

Pin-1 of 'HC164 is high. Pin-9 (clear) is high. Initially all outputs are zero and also clock pin-8 zero.

When I give a clock (from a monoshot) low-high, all the outputs of 'HC 164 are changing to high if the input pin-2 is high, or changing to low if pin-2 is low, whereas, I'm supposed to see a serial shift in the outputs. There's no setup time violation issue as I'm proving the inputs (data pin-2 and clock pin-9) manually. Also there's no clock jitters.

Can someone help explaining what's wrong? I don't think HC/LS interfacing is a problem- or is it? I tried 3-4 samples of 'HC164. All behave the same way.

Pin-1 of 'HC164 is high. Pin-9 (clear) is high. Initially all outputs are zero and also clock pin-8 zero.

When I give a clock (from a monoshot) low-high, all the outputs of 'HC 164 are changing to high if the input pin-2 is high, or changing to low if pin-2 is low, whereas, I'm supposed to see a serial shift in the outputs. There's no setup time violation issue as I'm proving the inputs (data pin-2 and clock pin-9) manually. Also there's no clock jitters.

Can someone help explaining what's wrong? I don't think HC/LS interfacing is a problem- or is it? I tried 3-4 samples of 'HC164. All behave the same way.