meeyaw

Junior Member level 3

- Joined

- Nov 29, 2010

- Messages

- 26

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,482

Hi edaboard people,

Please help me about this problem shown in the attachment image.

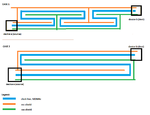

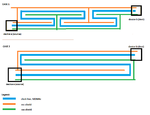

I have two possible routes for a clock line from device A to device B. As you can see, CASE A has more loop than case B. Both cases are shielded by vcc-vss pair.

The question is, which one is more prone to crosstalk: Case A or Case B? May I also know why is that so?

These cases confuses me already about which of them will I implement in layout.

Thanks for anyone who can answer it.

Please help me about this problem shown in the attachment image.

I have two possible routes for a clock line from device A to device B. As you can see, CASE A has more loop than case B. Both cases are shielded by vcc-vss pair.

The question is, which one is more prone to crosstalk: Case A or Case B? May I also know why is that so?

These cases confuses me already about which of them will I implement in layout.

Thanks for anyone who can answer it.