Vhdlontherise

Newbie

Hi everyone, i am facing a problem with a project in VHDL.

Part of the task is to implement a series of components that are each composed by a multiplier, developed with a behavioural architecture. This one receive two inputs but these are not always available at the same moment for every component.

Does VHDL syntax have a word to make my component wait for both inputs to be available? Being "a" and "b" the inputs i tried with different conditions but it won't work.

I tried for example with "a'event", "b'event", "a'event and b'event", i even tried with different conditions with nested if-sentences such as "if( a'event and b /= "U") then - if(b'event and a/="U")" (in my code the words have 8 bit so this latest one is a little bit different but it is just to give an idea).

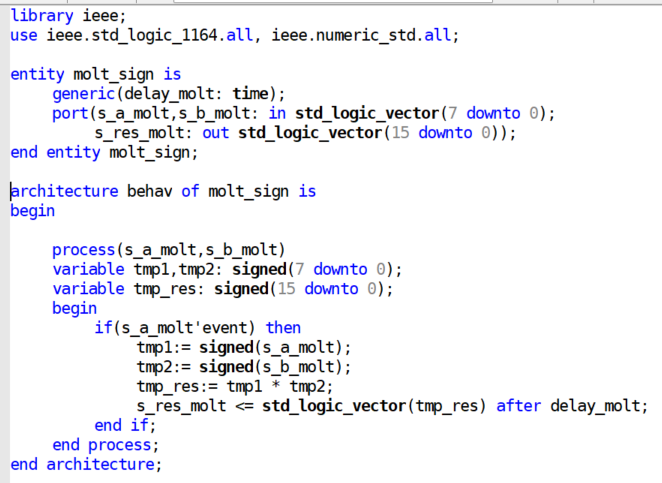

I'll share a pic of my code for the multiplier and the wave form of the signals.

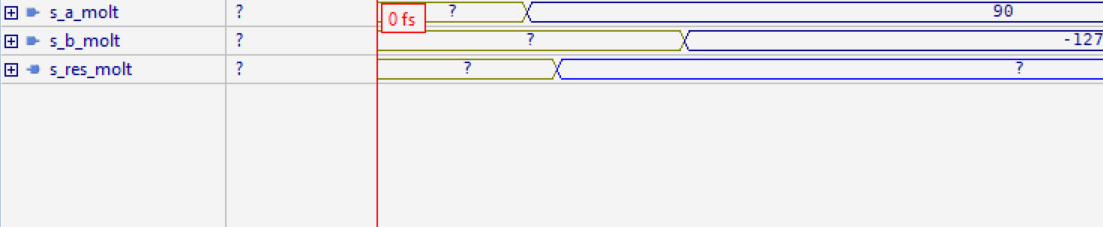

As you can see, since the input "s_a_molt" is available and "s_b_molt" is not, it doesn't calculate the result. (of course).

Thanks for your time

Part of the task is to implement a series of components that are each composed by a multiplier, developed with a behavioural architecture. This one receive two inputs but these are not always available at the same moment for every component.

Does VHDL syntax have a word to make my component wait for both inputs to be available? Being "a" and "b" the inputs i tried with different conditions but it won't work.

I tried for example with "a'event", "b'event", "a'event and b'event", i even tried with different conditions with nested if-sentences such as "if( a'event and b /= "U") then - if(b'event and a/="U")" (in my code the words have 8 bit so this latest one is a little bit different but it is just to give an idea).

I'll share a pic of my code for the multiplier and the wave form of the signals.

As you can see, since the input "s_a_molt" is available and "s_b_molt" is not, it doesn't calculate the result. (of course).

Thanks for your time