rajua

Newbie level 3

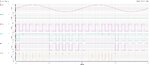

im designing double tail comparator for sar adc. Im getting clock signal when input voltage is above reference voltage. How to get low voltage when vin is below reference voltage. Why clock signal is getting triggered in the output signal instead of zero volts. Please reply me..