jeevaaraam

Member level 2

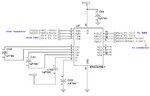

Re: RS422 communication failure at elevated temperature

The circuit (Single line diagram is attached)

The transceiver IC: AM26LS32AMDREP

The UART: XR16C864IQ

Both are operated at +5V DC.

- - - Updated - - -

The circuit (Single line diagram is attached)

The transceiver IC: AM26LS32AMDREP

The UART: XR16C864IQ

Both are operated at +5V DC.

The circuit (Single line diagram is attached)

The transceiver IC: AM26LS32AMDREP

The UART: XR16C864IQ

Both are operated at +5V DC.

- - - Updated - - -

The circuit (Single line diagram is attached)

The transceiver IC: AM26LS32AMDREP

The UART: XR16C864IQ

Both are operated at +5V DC.