AfiqahRS

Newbie level 3

Hi,

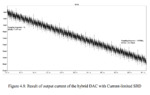

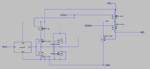

How can I improve glitches encountered on following DAC circuit? I have implemented an SRD (Swing Reduced Driver) to the circuit but somehow I need to reduce another 5% of these glitches. Any simple method that can be implemented? I have attached the circuit as well.

View attachment Schematic of Hybrid DAC.rar

How can I improve glitches encountered on following DAC circuit? I have implemented an SRD (Swing Reduced Driver) to the circuit but somehow I need to reduce another 5% of these glitches. Any simple method that can be implemented? I have attached the circuit as well.

View attachment Schematic of Hybrid DAC.rar