Anum72

Newbie level 4

- Joined

- Apr 10, 2012

- Messages

- 5

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,326

Hi!

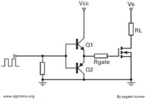

I am designing a shunt regulator which regulates the power from the solar panels. The power that is required by the loads is transferred from the solar panels to the loads and the extra power is dissipated through the shunt regulator unit. The circuit diagram is attached.

The comparator drives the MOSFET IRFZ44N (the datasheet is attached), when the bus voltage exceeds 28 volts the comparator gives high signal and MOSFET gets ON and extra power is shunted through the MOSFET.

Vsupply=12V

My problem is the MOSFETS are getting hot. The comparator having higher Vref (28.1V) gives pwm signal which is given at the gate. The pwm driven MOSFETS are getting hot. The comparator having Vref=28V gives ON signal that is 12V and its MOSFETS are not getting hot. Please help me out in finding the reason why the MOSFETS are getting hot. If anything related to the circuit is not clear please ask. Your help will highly be appreciated.

Thanks.

I am designing a shunt regulator which regulates the power from the solar panels. The power that is required by the loads is transferred from the solar panels to the loads and the extra power is dissipated through the shunt regulator unit. The circuit diagram is attached.

The comparator drives the MOSFET IRFZ44N (the datasheet is attached), when the bus voltage exceeds 28 volts the comparator gives high signal and MOSFET gets ON and extra power is shunted through the MOSFET.

Vsupply=12V

My problem is the MOSFETS are getting hot. The comparator having higher Vref (28.1V) gives pwm signal which is given at the gate. The pwm driven MOSFETS are getting hot. The comparator having Vref=28V gives ON signal that is 12V and its MOSFETS are not getting hot. Please help me out in finding the reason why the MOSFETS are getting hot. If anything related to the circuit is not clear please ask. Your help will highly be appreciated.

Thanks.