shredder929

Junior Member level 3

- Joined

- Jul 1, 2019

- Messages

- 27

- Helped

- 1

- Reputation

- 2

- Reaction score

- 2

- Trophy points

- 3

- Location

- Massachusetts

- Activity points

- 408

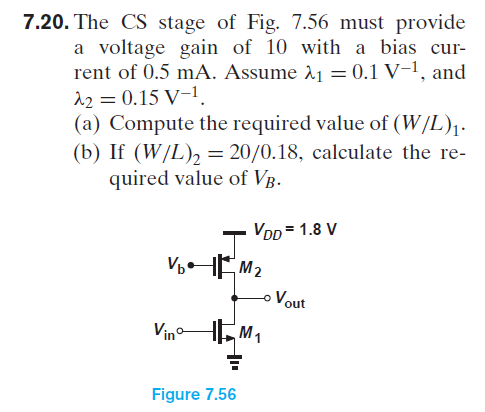

Not a homework problem, I'm refreshing before semester starts. Problem is from chapter 7 of Razavi Fundamentals. Given are Vth = 0.4V, un*Cox = 200uA/V^2, up*Cox = 100uA/V^2.

Part a I figured out, Av = gm1 * (ro1//ro2), and ro1 and ro2 are 1/(lamba * Id). That gets me gm1, and I set gm1 = sqrt(2 * un*Cox * (W/L)1 * Id) and solve for (W/L)1. I got 7.8125.

I'm now struggling on part b. The equation for bias Id of each transistor is 1/2u*Cox W/L * (VGS-VTH)^2 * (1 + lambda*VDS), both equal to each other (obviously using the PMOS version for the PFET)

Where I'm having problems is how I go about finding VGS for M1, and where Vout is biased at (i.e what is VDS or VSD?). The drain-source voltage for M1 and M2 add up to VDD but that's all I know. I was going to assume Vout sits at VDD/2 but that seems wrong. Any pointers?

Part a I figured out, Av = gm1 * (ro1//ro2), and ro1 and ro2 are 1/(lamba * Id). That gets me gm1, and I set gm1 = sqrt(2 * un*Cox * (W/L)1 * Id) and solve for (W/L)1. I got 7.8125.

I'm now struggling on part b. The equation for bias Id of each transistor is 1/2u*Cox W/L * (VGS-VTH)^2 * (1 + lambda*VDS), both equal to each other (obviously using the PMOS version for the PFET)

Where I'm having problems is how I go about finding VGS for M1, and where Vout is biased at (i.e what is VDS or VSD?). The drain-source voltage for M1 and M2 add up to VDD but that's all I know. I was going to assume Vout sits at VDD/2 but that seems wrong. Any pointers?