Tbit

Newbie level 3

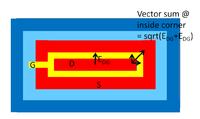

The enclosed gate layout (ELT)of a MOS transistor is a popular physical implementation in mitigating the effects of TID (ionising radiation) on normal device operation in Space/Cosmic environments.

A couple of questions:

1/ I would appreciate knowing where I can find detailed classic information on the principle of the MOS enclosed gate layout structure to mitigate TID effects?

2/ If the modelling of this ELT structure is accounted for in any BSIM/Compact Spice model then what are the parameters involved and how do they differ from the BSIM model of a normal MOS transistor layout?

A couple of questions:

1/ I would appreciate knowing where I can find detailed classic information on the principle of the MOS enclosed gate layout structure to mitigate TID effects?

2/ If the modelling of this ELT structure is accounted for in any BSIM/Compact Spice model then what are the parameters involved and how do they differ from the BSIM model of a normal MOS transistor layout?