cupoftea

Advanced Member level 5

Hi,

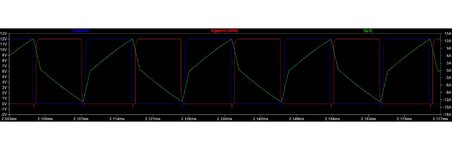

We have a 1kW Boost PFC followed by a Half Bridge. They are both driven by a ML4800 controller. The PFC is leading edge driven. That means, the PFC diode will conduct just as the Half bridge FET turns ON…..the problem is, our half bridge uses the transformer leakage inductor as the “output inductor”. As such, its waveforms are as attached (primary current and both FET gate drives). This shows that the ML4800 principle of reducing ripple in the PFC output caps simply doesn’t work for us….would you agree?

ML4800

We have a 1kW Boost PFC followed by a Half Bridge. They are both driven by a ML4800 controller. The PFC is leading edge driven. That means, the PFC diode will conduct just as the Half bridge FET turns ON…..the problem is, our half bridge uses the transformer leakage inductor as the “output inductor”. As such, its waveforms are as attached (primary current and both FET gate drives). This shows that the ML4800 principle of reducing ripple in the PFC output caps simply doesn’t work for us….would you agree?

ML4800