SamV

Newbie level 6

Hi all,

I hope some of you find this interesting..

We have 2 prototypes, one at our company and another using a different hardware platform at another company. The routing of the prototype at the other company has LVDS traces which are >= 15cm, the ADC operates at 250MHZ and were routing the LVDS pairs to an FPGA.

The data from our prototype looks fine, however there are big problems in the data from the other prototype. I know two things about the routing on the prototype at the other company, the pcb/traces are not impedance controlled and the trace lengths between bits (e.g. LVDS bit 9 and LVDS bit 8) may not be length matched. I'm trying to get my head around what the results from the converter after being acquired by the FPGA may look like if there are reflections. After doing a little research I'm thinking reflections may be causing jitter.

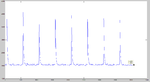

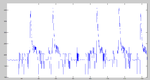

I've attached two images, one is sampled data acquired from prototype 1 at our company, the second is sampled data acquired by prototype 2 at the other company. These are digitized waveforms from a nuclear detector. You will notice that one of the two plots has obvious noise issues.

Keeping it simple, please look at the good plot and tell me what I might expect to see different in the basic example of an impedance mismatch (i.e. unknown differential resistance between the + and - differential pairs on the PCB) I'm having a tricky time visualizing this.

Looking at the bad looking plot, does anyone think this looks like what they may have seen before when experiencing LVDS reflection issues? I'd like to say for sure that the problem is something to do with not following the LVDS specs when routing the PCB.

Thanks,

Sam

I hope some of you find this interesting..

We have 2 prototypes, one at our company and another using a different hardware platform at another company. The routing of the prototype at the other company has LVDS traces which are >= 15cm, the ADC operates at 250MHZ and were routing the LVDS pairs to an FPGA.

The data from our prototype looks fine, however there are big problems in the data from the other prototype. I know two things about the routing on the prototype at the other company, the pcb/traces are not impedance controlled and the trace lengths between bits (e.g. LVDS bit 9 and LVDS bit 8) may not be length matched. I'm trying to get my head around what the results from the converter after being acquired by the FPGA may look like if there are reflections. After doing a little research I'm thinking reflections may be causing jitter.

I've attached two images, one is sampled data acquired from prototype 1 at our company, the second is sampled data acquired by prototype 2 at the other company. These are digitized waveforms from a nuclear detector. You will notice that one of the two plots has obvious noise issues.

Keeping it simple, please look at the good plot and tell me what I might expect to see different in the basic example of an impedance mismatch (i.e. unknown differential resistance between the + and - differential pairs on the PCB) I'm having a tricky time visualizing this.

Looking at the bad looking plot, does anyone think this looks like what they may have seen before when experiencing LVDS reflection issues? I'd like to say for sure that the problem is something to do with not following the LVDS specs when routing the PCB.

Thanks,

Sam