PrescottDan

Banned

- Joined

- May 1, 2014

- Messages

- 119

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 16

- Activity points

- 0

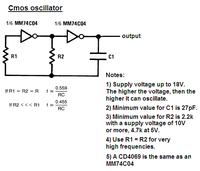

A Timer circuit, Oscillator circuit or a Clock circuit output a TTL logic signals

When the Power supply voltages varies higher , the output of the Timing signal gets Faster

When the power supply voltage varies lower, the output of the timing signal gets slower

Why does this happen?

What else can cause the Timing signals to get faster or slower?

When the Power supply voltages varies higher , the output of the Timing signal gets Faster

When the power supply voltage varies lower, the output of the timing signal gets slower

Why does this happen?

What else can cause the Timing signals to get faster or slower?