red_0220

Junior Member level 1

Hi all, I plan to change data of cell library ,

I must know what are These value mean.

Please help me to confirm whether error in These Figures.

This is D-Flip Flop(DFF) data of cell library :

cell(QDFFLTX1) {

area : 17.00;

cell_footprint : "QDFF" ;

ff(IQ, IQN) {

next_state : "D";

clocked_on : "CK";

.

.

.

pin(Q) {

.

.

.

}

pin(D) {

nextstate_type : data;

direction : input ;

capacitance : 0.0007691;

timing() {

related_pin : "CK";

sdf_edges : both_edges;

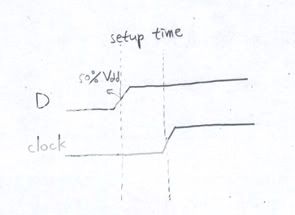

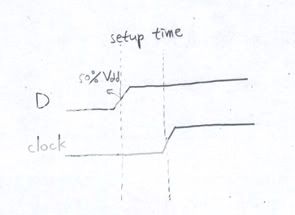

timing_type : setup_rising;

rise_constraint(CONST_3x3) {

index_1("0.006000,0.217000,0.434000");

index_2("0.006000,0.108000,0.217000");

values("0.004,0.001,-0.22",\

"0.14,0.004,-0.12",\

"0.22,0.09,-0.03");

}

Is value a representative setup time between D and CK?

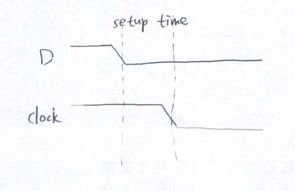

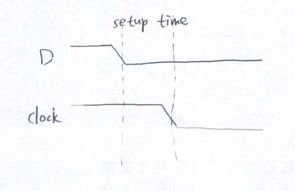

fall_constraint(CONST_3x3) {

index_1("0.006000,0.217000,0.434000");

index_2("0.006000,0.108000,0.217000");

values("0.5915,0.5915,0.6669",\

"0.4860,0.4860,0.5614",\

"0.3964,0.3964,0.4538");

}

Is value a representative setup time between D and CK?

}

timing() {

related_pin : "CK";

sdf_edges : both_edges;

timing_type : hold_rising;

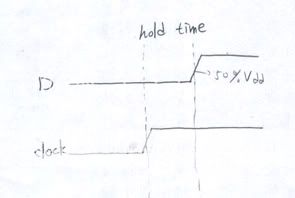

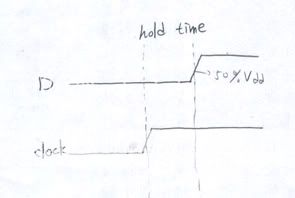

rise_constraint(CONST_3x3) {

index_1("0.006000,0.217000,0.434000");

index_2("0.006000,0.108000,0.217000");

values("0.07376,0.07376,0.1023",\

"0.07387,0.07387,0.1024",\

"0.07616,0.07616,0.1025");

}

Is value a representative hold time between D and CK?

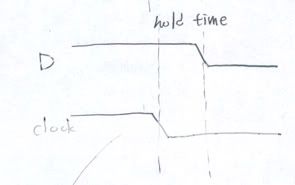

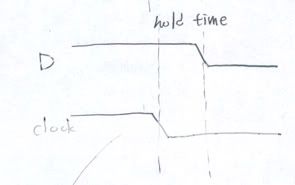

fall_constraint(CONST_3x3) {

index_1("0.006000,0.217000,0.434000");

index_2("0.006000,0.108000,0.217000");

values("0.09,0.09,0.12",\

"0.09,0.09,0.12",\

"0.11,0.11,0.12");

}

Is value a representative hold time between D and CK?

}

}

.

.

.

Everywhere needs revising?

I must know what are These value mean.

Please help me to confirm whether error in These Figures.

This is D-Flip Flop(DFF) data of cell library :

cell(QDFFLTX1) {

area : 17.00;

cell_footprint : "QDFF" ;

ff(IQ, IQN) {

next_state : "D";

clocked_on : "CK";

.

.

.

pin(Q) {

.

.

.

}

pin(D) {

nextstate_type : data;

direction : input ;

capacitance : 0.0007691;

timing() {

related_pin : "CK";

sdf_edges : both_edges;

timing_type : setup_rising;

rise_constraint(CONST_3x3) {

index_1("0.006000,0.217000,0.434000");

index_2("0.006000,0.108000,0.217000");

values("0.004,0.001,-0.22",\

"0.14,0.004,-0.12",\

"0.22,0.09,-0.03");

}

Is value a representative setup time between D and CK?

fall_constraint(CONST_3x3) {

index_1("0.006000,0.217000,0.434000");

index_2("0.006000,0.108000,0.217000");

values("0.5915,0.5915,0.6669",\

"0.4860,0.4860,0.5614",\

"0.3964,0.3964,0.4538");

}

Is value a representative setup time between D and CK?

}

timing() {

related_pin : "CK";

sdf_edges : both_edges;

timing_type : hold_rising;

rise_constraint(CONST_3x3) {

index_1("0.006000,0.217000,0.434000");

index_2("0.006000,0.108000,0.217000");

values("0.07376,0.07376,0.1023",\

"0.07387,0.07387,0.1024",\

"0.07616,0.07616,0.1025");

}

Is value a representative hold time between D and CK?

fall_constraint(CONST_3x3) {

index_1("0.006000,0.217000,0.434000");

index_2("0.006000,0.108000,0.217000");

values("0.09,0.09,0.12",\

"0.09,0.09,0.12",\

"0.11,0.11,0.12");

}

Is value a representative hold time between D and CK?

}

}

.

.

.

Everywhere needs revising?