melkord

Full Member level 3

Hi,

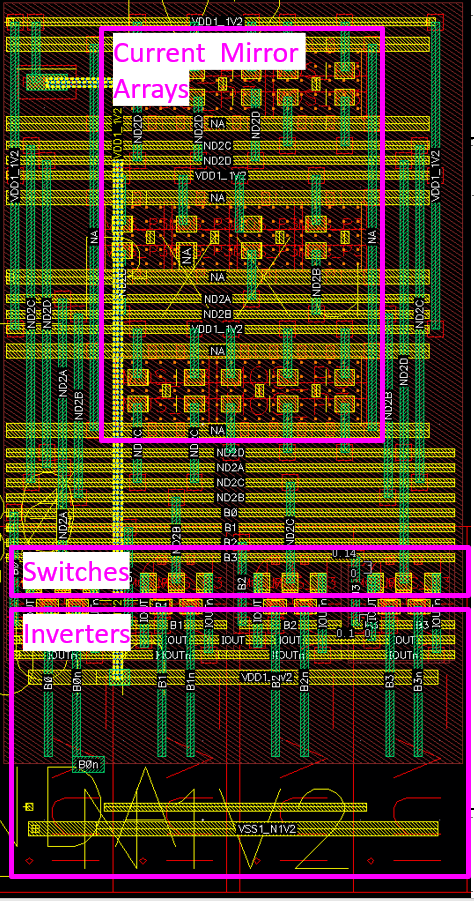

Any tips to reduce the area of current-output current-steering DAC? or maybe better floorplan?

I feel that the current mirror arrays takes so much space but not sure how to make it better.

Here is my layout:

Any tips to reduce the area of current-output current-steering DAC? or maybe better floorplan?

I feel that the current mirror arrays takes so much space but not sure how to make it better.

Here is my layout: