Enshuo

Junior Member level 2

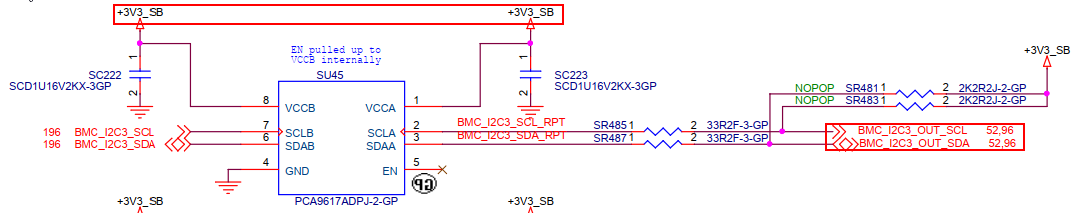

Hi,

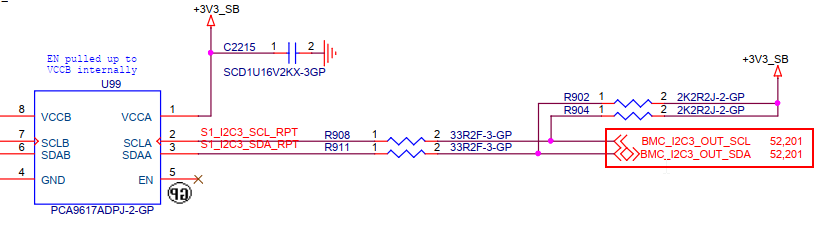

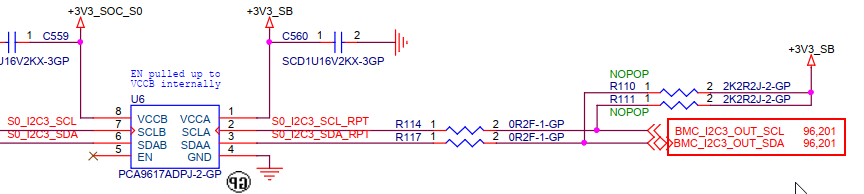

I study the I2C divides into two nets with a repeater PCA9617ADPJ below (BMC_I2C3_SCL -> BMC_I2C3_OUT_SCL). Every kind of I2C is the same. It looks it's only for buffering (rise/fall time, not voltage shifting). Is it really needed?

Repeater datasheet https://www.nxp.com/docs/en/data-sheet/PCA9617A.pdf

I study the I2C divides into two nets with a repeater PCA9617ADPJ below (BMC_I2C3_SCL -> BMC_I2C3_OUT_SCL). Every kind of I2C is the same. It looks it's only for buffering (rise/fall time, not voltage shifting). Is it really needed?

Repeater datasheet https://www.nxp.com/docs/en/data-sheet/PCA9617A.pdf