Easy peasy

Advanced Member level 6

can you post your corrected schematic?

- - - Updated - - -

Delete C7, C10 in your sim...

- - - Updated - - -

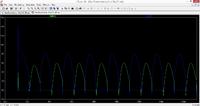

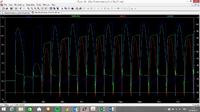

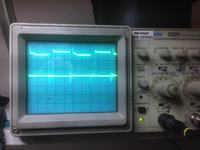

and vary the freq until things look right, there is only one freq where the circuit is single cycle resonant - you want to be just above that. 1.555MHz, or 1.04 MHz (1.5 rings of the power circuit) or, 778kHz, (2 rings of the power circuit)

- - - Updated - - -

Delete C7, C10 in your sim...

- - - Updated - - -

and vary the freq until things look right, there is only one freq where the circuit is single cycle resonant - you want to be just above that. 1.555MHz, or 1.04 MHz (1.5 rings of the power circuit) or, 778kHz, (2 rings of the power circuit)