Junus2012

Advanced Member level 5

- Joined

- Jan 9, 2012

- Messages

- 1,552

- Helped

- 47

- Reputation

- 98

- Reaction score

- 53

- Trophy points

- 1,328

- Location

- Italy

- Activity points

- 15,235

Hello all

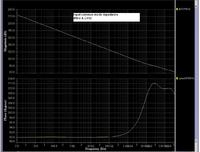

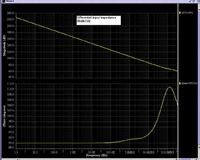

I am trying to simulate the input differential resistance and capacitance for my operational amplifier.

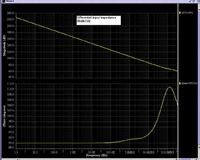

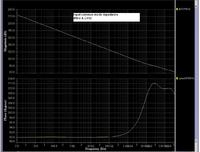

I am also trying to simulate the common mode input resistance and capacitance.

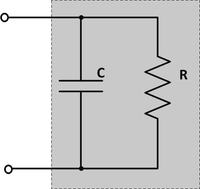

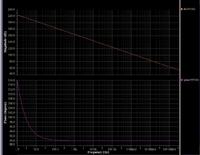

I assumed that both of the resistance and the capacitance are in parallel, so I connected a current source and I run the AC simulation. I got theses two result but it seems al little strange for me

I am looking for your help

Regards

I am trying to simulate the input differential resistance and capacitance for my operational amplifier.

I am also trying to simulate the common mode input resistance and capacitance.

I assumed that both of the resistance and the capacitance are in parallel, so I connected a current source and I run the AC simulation. I got theses two result but it seems al little strange for me

I am looking for your help

Regards