student_078

Newbie level 5

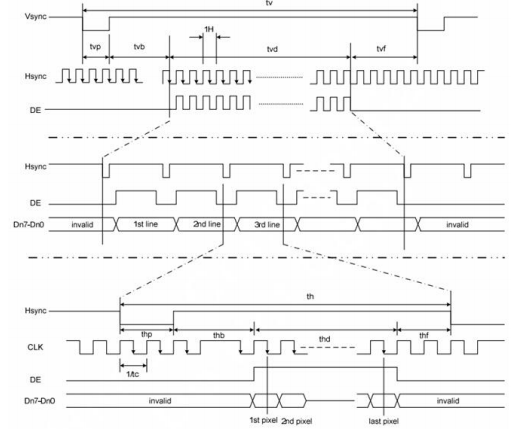

I use the Vsync/Hsync/DE/CLK to interface to LCD displays. Typical waveform is as below.

In the FPGA design vendor provided, the data is discontinuous and the DE is used to enable each pixel. Within each line Hsync, there are always 1024 pixels, but with a few CLK of breaks.

Vsync/Hsync timing are accurate.

Would that FPGA work for mainstream display panels? If not what kind of situations would I observe on screen?

In the FPGA design vendor provided, the data is discontinuous and the DE is used to enable each pixel. Within each line Hsync, there are always 1024 pixels, but with a few CLK of breaks.

Vsync/Hsync timing are accurate.

Would that FPGA work for mainstream display panels? If not what kind of situations would I observe on screen?